# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministériel: 25 mai 2016

Présentée par

# Raphaël BLEUSE

Thèse dirigée par **Denis TRYSTRAM** et codirigée par **Grégory Mouni**É

préparée au sein du **Laboratoire d'Informatique de Grenoble** et de l'École Doctorale **MSTII**

# Appréhender l'hétérogénéité à (très) grande échelle

Apprehending heterogeneity at (very) large scale

Thèse soutenue publiquement le **11 octobre 2017**, devant le jury composé de :

#### **Lionel EYRAUD-DUBOIS**

Chargé de Recherche, LaBRI, Inria, France, Examinateur

#### **Nectarios Koziris**

Professeur d'Université, School of Electrical and Computer Engineering, National Technical University of Athens, Grèce, Rapporteur

#### Vitus J. LEUNG

Principal Member of Technical Staff, Sandia National Laboratories, États-Unis, Rapporteur

#### Grégory Mounié

Maître de Conférences, LIG, Univ. Grenoble Alpes, France, Co-Directeur de thèse

#### Alix MUNIER

Professeure d'Université, LIP6, UPMC, France, Examinatrice

#### **Yves Robert**

Professeur d'Université, LIP, ENS Lyon, France, Président

#### **Denis Trystram**

Professeur d'Université, LIG, Univ. Grenoble Alpes, France, Directeur de thèse

L'expression est œuvre difficile, lente et tortueuse,

— et l'erreur est de croire que n'est pas ce qui ne

peut d'abord s'énoncer.

— Antoine de Saint-Exupéry

# Remerciements

(Acknowledgments)

I would like to first thank the jury members, and especially the two reviewers Nectarios Koziris and Vitus J. Leung who provided insightful comments on my dissertation. I would like to thank the DGA-MRIS for the scholarship they granted me. I would like to thank the JLESC for funding my travels to the USA. I am grateful to the NCSA members who welcomed me; notably Greg Bauer, Jeremy Enos, Andriy Kot, and Sharif Islam.

Mes travaux de thèse ne seraient pas ce qu'ils sont sans Denis et Grégory. Je souhaite chaudement remercier Denis pour ses conseils avisés et sa patience. Je remercie Grégory pour son enthousiame, son optimisme à toute épreuve et son foisonnement d'idées. Je souhaite aussi vivement remercier les collègues des deux équipes MESCAL/MOAIS (ou plutôt DATAMOVE/POLARIS) pour l'environnement exceptionnel de recherche qu'ils arrivent à faire vivre. Merci en particulier à Jean-Marc de m'avoir integré dans ton effort de médiation. Merci aussi à Olivier et Florence pour ces discussions de cafét' pendant cet été de rédaction. Annie tient aussi une place spéciale au travers du soutien quotidien qu'elle apporte aux deux équipes. Merci à Alexis, David et David, thésards du bureau 443 pour ces moments de travail/rédaction/codage/discussion/etc. partagés. Je ne remercie pas Millian afin de mieux le troller¹. Une attention spéciale va à Fernando, en qui j'ai trouvé un frère brésilien habile du fer souder mais rétif au français.

Un grand merci aussi à mes parents ainsi qu'à mes deux sœurs pour leur compagnie, soutien, dessins, etc.

Je tiens aussi à remercier mes compagnes et compagnons de liberté—que sont notamment Hélène, Manu, Pauline et Sylvain-Lio'—pour ces aventures verticales et spirituelles qui ont marqué ces dernières années.

Enfin, merci à Mathou d'Être qui Elle Est.

<sup>&</sup>lt;sup>1</sup>Vous aurez, bien entendu, saisi le ton ironique.

# Abstract / Résumé

### **Abstract**

The demand for computation power is steadily increasing, driven by the need to simulate more and more complex phenomena with an increasing amount of consumed/produced data. To meet this demand, the High Performance Computing platforms grow in both size and heterogeneity. Indeed, heterogeneity allows splitting problems for a more efficient resolution of sub-problems with *ad hoc* hardware or algorithms. This heterogeneity arises in the platforms' architecture and in the variety of processed applications. Consequently, the performances become more sensitive to the execution context.

We study in this dissertation how to qualitatively bring—at a reasonable cost—context-awareness/obliviousness into allocation and scheduling policies. This study is conducted from two standpoints: within single applications, and at the whole platform scale from an inter-applications perspective.

We first study the minimization of the *makespan* of sequential tasks on platforms with a mixed architecture composed of multiple CPUs and GPUs. We integrate context-awareness into schedulers with an affinity mechanism that improves local behavior. This mechanism has been implemented in a parallel run-time, and experiments show that it is able to reduce the memory transfers while maintaining a low makespan. We then extend the model to implicitly consider parallelism on the CPUs with the moldable-task model. We propose an efficient algorithm formulated as an integer linear program with a constant performance guarantee of  $\frac{3}{2} + \epsilon$ .

Second, we devise a new modeling framework where constraints are a first-class tool. Rather than extending existing models to consider all possible interactions, we reduce the set of feasible schedules by further constraining existing models. We propose a set of reasonable constraints to model application spreading and I/O traffic. We then instantiate this framework for unidimensional topologies, and propose a comprehensive case study of the makespan minimization under convex and local constraints.

#### Résumé

Le besoin de simuler des phénomènes toujours plus complexes accroît les besoins en puissance de calcul, tout en consommant et produisant de plus en plus de données. Pour répondre à cette demande, la taille et l'hétérogénéité des plateformes de calcul haute performance augmentent. L'hétérogénéité permet en effet de découper les problèmes en sous-problèmes, pour lesquels du matériel ou des algorithmes *ad hoc* sont plus efficients. Cette hétérogénéité se manifeste dans l'architecture des plateformes et dans la variété des applications exécutées. Aussi, les performances sont de plus en plus sensibles au contexte d'exécution.

L'objet de cette thèse est de considérer, qualitativement et à faible coût, l'impact du contexte d'exécution dans les politiques d'allocation et d'ordonnancement. Cette étude est menée à deux niveaux : au sein d'applications uniques, et à l'échelle des plateformes au niveau inter-applications.

Nous étudions en premier lieu la minimisation du temps de complétion pour des tâches séquentielles sur des plateformes hybrides intégrant des CPU et des GPU. Nous proposons de tenir compte du contexte d'exécution grâce à un mécanisme d'affinité améliorant le comportement local des politiques d'ordonnancement. Ce mécanisme a été implémenté dans un *run-time* parallèle. Une campagne d'expérience montre qu'il permet de diminuer les transferts de données tout en conservant un faible temps de complétion. Puis, afin de prendre implicitement en compte le parallélisme sur les CPU, nous enrichissons le modèle en considérant les tâches comme *moldables* sur CPU. Nous proposons un algorithme basé sur la programmation linéaire en nombres entiers. Cet algorithme efficace a un rapport de compétitivité de  $\frac{3}{2} + \epsilon$ .

Dans un second temps, nous proposons un nouveau cadre de modélisation dans lequel les contraintes sont des outils de premier ordre. Plutôt que d'étendre les modèles existants en considérant toutes les interactions possibles, nous réduisons l'espace des ordonnancements réalisables via l'ajout de contraintes. Nous proposons des contraintes raisonnables pour modéliser l'étalement des applications ainsi que les flux d'E/S. Nous proposons ensuite une étude de cas exhaustive dans le cadre de la minimisation du temps de complétion pour des topologies unidimensionnelles, sous les contraintes de convexité et de localité.

# Contents

| A  | cknow  | /ledgme | ents                                                  | ٧    |

|----|--------|---------|-------------------------------------------------------|------|

| Αl | ostrac | t / Ré  | sumé                                                  | vii  |

| Co | onten  | ts      |                                                       | ix   |

| 1  | Intro  | oductio | on                                                    | 1    |

|    | 1.1    | Backg   | round                                                 | 1    |

|    | 1.2    | Conte   | xtualization                                          | 2    |

|    |        | 1.2.1   | Intra-Application Level                               | 5    |

|    |        | 1.2.2   | Inter-Applications Level                              | 5    |

|    | 1.3    | Explic  | it vs. Implicit Modeling of Communications            | 6    |

|    |        | 1.3.1   | Existing Explicit Models                              | 7    |

|    |        | 1.3.2   | Limits of Explicit Models                             | 8    |

|    |        | 1.3.3   | Implicit Modeling                                     | 8    |

|    | 1.4    | Contri  | butions                                               | 9    |

|    | 1.5    | Conte   | nt                                                    | . 12 |

| 2  | Sch    | eduling | Independent Sequential Tasks on Multi-Cores with GPUs | 15   |

|    | 2.1    | Proble  | em Definition                                         | . 17 |

|    | 2.2    | Relate  | d Work                                                | . 17 |

|    |        | 2.2.1   | Algorithmic Results                                   | . 17 |

|    |        | 2.2.2   | Parallel Run-times                                    | . 19 |

|    | 2.3    | XKaap   | oi Scheduling Framework                               | . 20 |

|    |        | 2.3.1   | Execution Flow                                        | . 21 |

|    |        | 2.3.2   | Performance Model                                     | . 21 |

|    | 2.4    | Sched   | uling Policies                                        | . 22 |

|    |        | 2.4.1   | HEFT: Heterogeneous Earliest-Finish-Time              | . 22 |

|    |        | 2.4.2   | Dual Approximation Based Algorithms                   | . 23 |

|    |        |         | Pure Dual Approach                                    | . 24 |

|    |        |         | Bringing Context-Awareness in: Affinity               | . 24 |

|    | 2.5    | Usabil  | ity of Scheduling Policies for Linear Algebra         | . 27 |

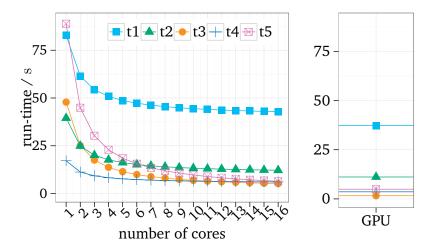

|   | 2.6  | Perfor  | mance Evaluation                                    | 29 |

|---|------|---------|-----------------------------------------------------|----|

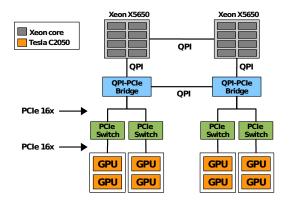

|   |      | 2.6.1   | Experimental Setup: Platform and Benchmarks         | 29 |

|   |      |         | Platform                                            | 29 |

|   |      |         | Benchmarks                                          | 29 |

|   |      |         | Methodology                                         | 30 |

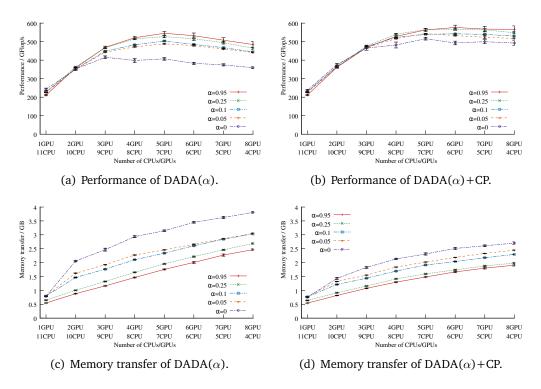

|   |      | 2.6.2   | Impact of the Affinity Control Parameter $\alpha$   | 30 |

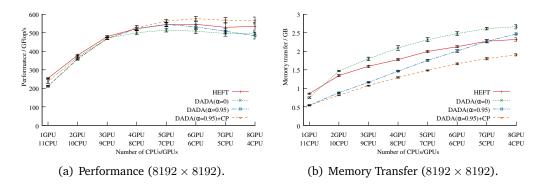

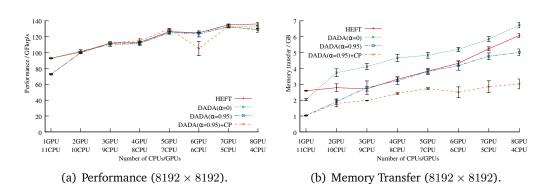

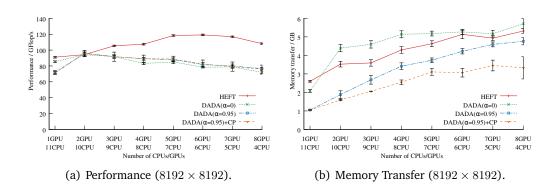

|   |      | 2.6.3   | Comparison of Scheduling Policies                   | 31 |

|   |      |         | Experimental Evaluation                             | 32 |

|   |      |         | Discussion                                          | 32 |

|   | 2.7  | Summ    | nary                                                | 34 |

| 3 | Scho | eduling | Independent Moldable Tasks on Multi-Cores with GPUs | 37 |

|   | 3.1  | Proble  | em Definition                                       | 38 |

|   | 3.2  | Relate  | ed Work                                             | 40 |

|   | 3.3  | Algori  | thm APPROX-3/2                                      | 41 |

|   |      | 3.3.1   | Partitioning Tasks                                  | 41 |

|   |      | 3.3.2   | Mathematical Formulation                            | 43 |

|   |      |         | Objective Function and Constraints                  | 43 |

|   |      |         | Filtering                                           | 44 |

|   |      |         | Integer Linear Program                              | 46 |

|   | 3.4  | Analys  | sis of the Algorithm APPROX-3/2                     | 46 |

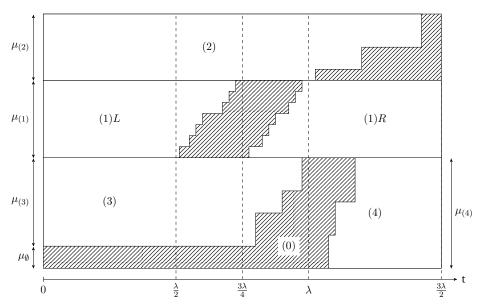

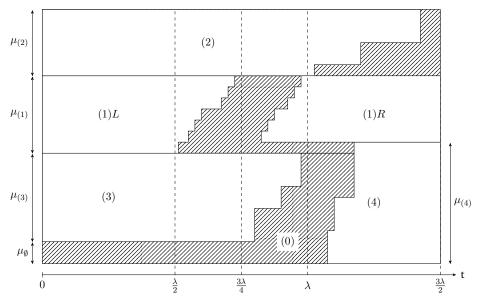

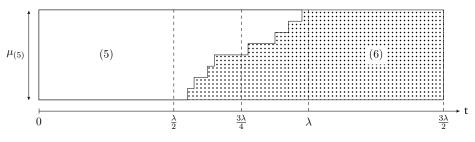

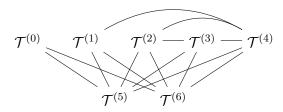

|   |      | 3.4.1   | Structure of a Schedule of Makespan $\lambda$       | 47 |

|   |      | 3.4.2   | Structure of the Partitioning                       | 48 |

|   |      | 3.4.3   | Correctness of the Dual Approximation               | 51 |

|   |      | 3.4.4   | Building the Schedule                               | 54 |

|   | 3.5  | Algori  | thm APPROX-2                                        | 54 |

|   |      | 3.5.1   | Sketch                                              | 55 |

|   |      | 3.5.2   | Analysis                                            | 55 |

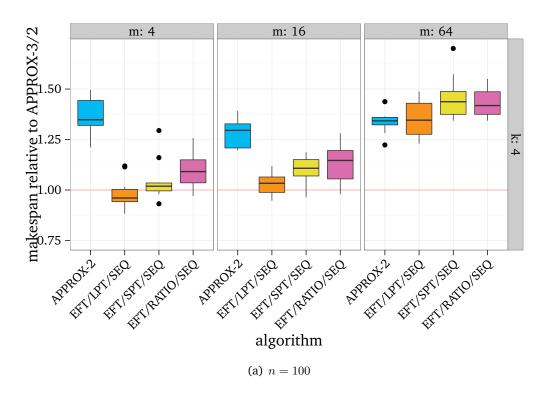

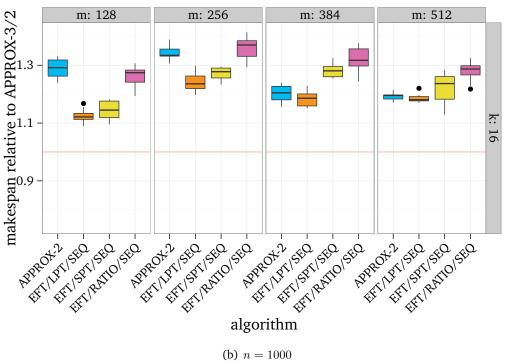

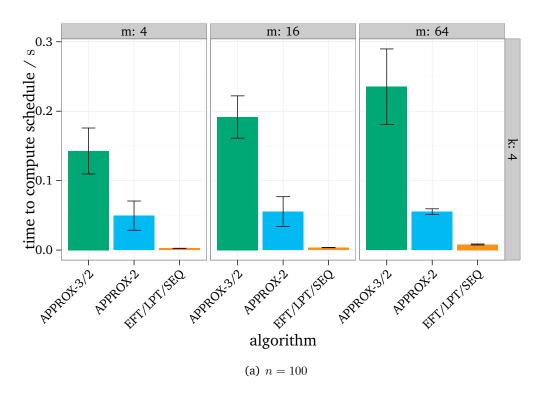

|   | 3.6  | Experi  | imental Evaluation                                  | 56 |

|   |      | 3.6.1   | Problem Instances                                   | 56 |

|   |      | 3.6.2   | HEFT-like Heuristics                                | 59 |

|   |      | 3.6.3   | Implementation Details                              | 60 |

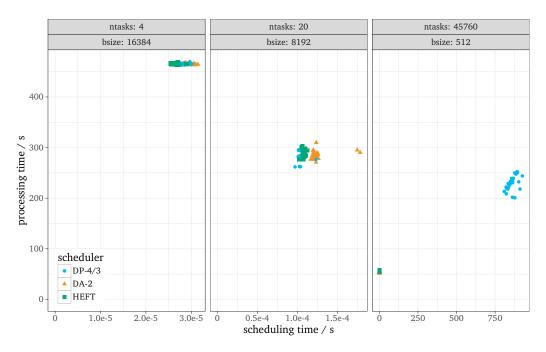

|   |      | 3.6.4   | Experimental Results                                | 61 |

|   | 3.7  | Summ    | nary                                                | 65 |

| 4 | Geo  | metric  | Constraints as a First-Class Modeling Tool          | 67 |

|   | 4.1  | Gener   | al Problem Setting                                  | 68 |

|   |      | 4.1.1   | Intrinsic Constraints                               | 70 |

|   |      | 4.1.2   | Extrinsic Metrics                                   | 74 |

|     |       | 4.1.3   | Extension of Graham Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 75 |

|-----|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

|     | 4.2   | Relate  | ed Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 76 |

| 5   | Unio  | dimensi | ional Problem's Instantiations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 79 |

|     | 5.1   | Forma   | ll Instantiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 79 |

|     |       | 5.1.1   | Structural Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 80 |

|     | 5.2   | Study   | of unpinned I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 81 |

|     |       | 5.2.1   | Complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 81 |

|     |       | 5.2.2   | Meta Approximation Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 82 |

|     |       |         | Sketch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 83 |

|     |       |         | Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 83 |

|     | 5.3   | Study   | of pinned I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 84 |

|     |       | 5.3.1   | Complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 84 |

|     |       | 5.3.2   | Approximation Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 86 |

|     |       |         | Algorithm with a single I/O node per job                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 86 |

|     |       |         | Analysis with a single I/O node per job                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 90 |

|     |       |         | Extending to any number of I/O nodes per job                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 92 |

|     | 5.4   | Summ    | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 95 |

| 6   | Con   | clusion | and Future Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 97 |

| •   |       |         | e Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 98 |

|     | 0.1   | ruture  | у отсерватительный положения в отсерватительный положения в отсерватительный положения в отсерватительный в отсерватительным в | • | 70 |

| Bi  | bliog | raphy   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | Α1 |

| Lis | st of | Figures | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P | 11 |

| Lis | st of | Tables  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A | 13 |

Introduction

# 1.1 Background

In High Performance Computing (HPC), the demand for computation power is steadily increasing, driven by the need to simulate more and more complex phenomena (structures at the atomic level, protein folding, fluid dynamics, etc.) with an increasing amount of consumed/produced data. In the near future, the great challenge for the HPC community is to build the ecosystem for both  $exaflop~(10^{18}~{\rm Flop/s})$  and  $sustained~petaflop~(10^{15}~{\rm Flop/s})$  performance levels. To measure up to such a challenge while keeping both construction and operating costs at a minimum, the HPC platforms (or supercomputers) require disruptive evolutions [Don+11]. Among these evolutions, two aspects require particular attention: scale~ and scale~

First, the extreme scale of the platforms is a challenge on its own. To absorb the demand in computing power, the platforms now integrate about ten million computing cores [@top500]. Still, increasing the number of cores is not sufficient as it only tackles the question of the available raw theoretical processing power. At such an extreme scale, the issues of feeding input data to the cores and retrieving the produced resulting data become the predominant difficulty. Due to the cost and scaling constraints, most of the current supercomputers have a unique and multipurpose interconnection network. These networks, such as the DragonFly or SlimFly interconnects [Kat+15], are usually organized as very dense local subnetworks that are interconnected by a global sparse network. Such topologies further emphasize the effects of locality.

Second, the platforms and their usages are growing in heterogeneity. This heterogeneity arises from various factors:

- The tremendous amount of data transiting in the platforms requires dedicated nodes within the platform to handle the generated load. It is indeed impossible for the computing nodes to keep in their local memories all the data required for computations.

- The platforms are now hybrid systems built with computing cores of various architectures. For example, the platforms may integrate slow general purpose

cores, or CPUs; efficient SIMD cores, such as GPUs or MICs; programmable cores dedicated to complex specific computations, or FPGAs; etc.

- The various network traffics induced by the applications share a unique network resource.

- The applications running on the platforms vary in many ways: their size, the time to process them, their communication patterns, etc.

As of today, the most efficient, state-of-the-art HPC platforms are able to achieve power efficiency in the order of  $10^{10} \,\mathrm{Flop/s\,W^{-1}}$  [@green500]. A quick calculation leads to an estimated power consumption of 100 MW for an exascale platform. Due to the ever-increasing power generation costs, such a tremendous power consumption for a single platform is not reasonable, and justifies the need for disruptions. However, we do not directly target the power consumption. We rather look at it through the prism of communications: communications, and more precisely data movements, are indeed the most power hungry operations. As a consequence, optimizing data movements will lower power consumption, but is particularly challenging for two reasons. First, as aforementioned, the volume of data is tremendous: the biggest applications routinely manage volumes of  $10\,\mathrm{TB}$  to  $100\,\mathrm{TB}$ . Such volume of data considerably stresses the interconnection network, and this volume of data is expected to follow the growth of applications and platforms. Second, the gap between memory, network and processor speeds is widening. This gap is such that applications, if not properly scheduled, spend more time waiting for data than computing [Ash+10].

# 1.2 Contextualization

By essence, any *model* reduces the object under study to a simpler set of characteristics, parameters and postulates. While this reduction is mandatory to apprehend the studied object, it is done at the cost of losing accuracy. In the case of executing applications on modern parallel platforms, phenomena such as network contention, complex data dependencies, memory hierarchies or tightly coupled tasks often are not modeled, though they have a huge impact on performance. We define *context* as such external elements that are not included into the model, but still have a significant impact. **The governing idea of this dissertation is to bring—at a reasonable cost—context awareness, or even context obliviousness, in the scheduling policies.** This idea is derived at two levels: within a single application at a fine grain scale, and with multiple concurrent applications at a coarser level.

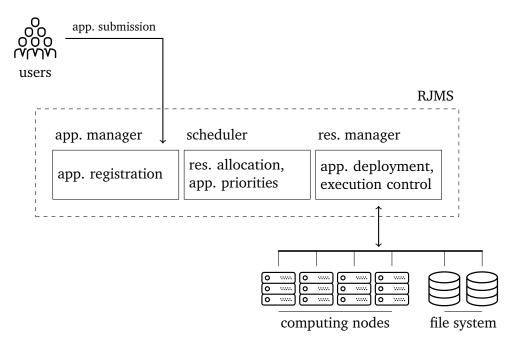

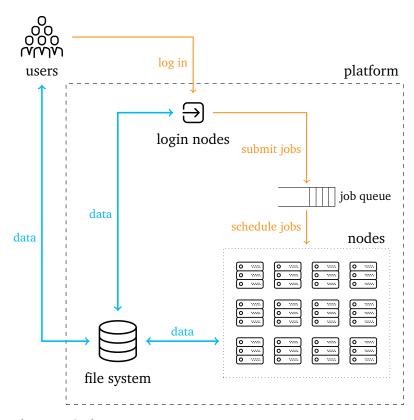

Figure 1.1 Overview of an application submission process on a typical parallel platform [Geo10]. The application manager is the interface between the users and the scheduler: the users send the description of their applications to the application manager. The resource manager is the interface between the scheduler and the platform: it monitors the resources, deploy applications, and control the execution of the applications. With respect to the resources status reported by the resource manager, the scheduler decides where (which resources to allocate) and when an application will execute. [Credits: icons by Madebyoliver and Zlatko Najdenovski; https://www.flaticon.com]

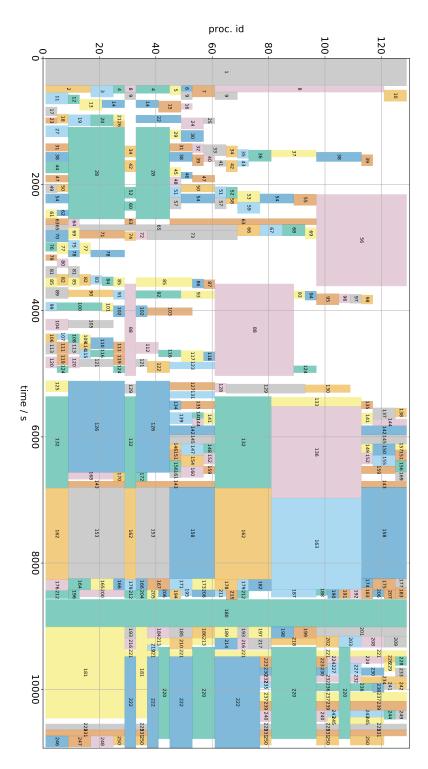

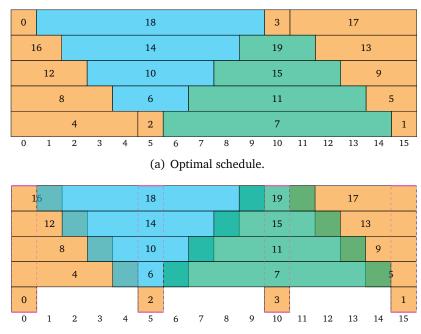

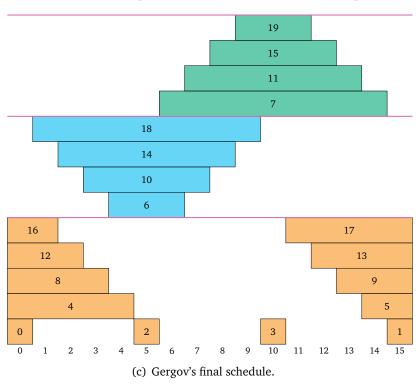

Before detailing both levels, let us sketch an application execution. When users of a parallel platform want to run an application, they submit the description of the application to the RJMS (Resource and Job Management System). An application description usually consists in an executable, resources requirements, and an estimation of the time needed to run the application. The RJMS is responsible for managing the applications (collecting users' requests, queuing applications), scheduling them (allocating resources to the applications), and managing the resources (deploying and starting applications). The critical role of the scheduler component is to satisfy the users' demand for computation by allocating some resources of the platform for some amount of time to their applications. An overview of an application submission process on a parallel platform is depicted on Figure 1.1. The decisions of the scheduler are often visualized as Gantt charts, as shown on Figure 1.2.

Figure 1.2 Gantt chart of a typical HPC workload. Jobs executed by processors (y-axis) are depicted by rectangles along the time line (x-axis). This chart represents the execution of 250 jobs on a platform with 128 processors. Two distinct phases are visible: the system starts to populate during a transient phase until the processors are saturated (around  $5000 \, \mathrm{s}$ ), the system then enter a steady state and processors are almost always used.

#### 1.2.1 Intra-Application Level

From the RJMS point of view, an application may be viewed as a black box (as depicted by rectangles on the Gantt chart on Figure 1.2), and we do not want to open this Pandora's box. Once some resources have been allocated to an application, the application itself is responsible for their correct usage.

An application is usually described as a set of tasks to process. These tasks are the core concept at this level: they represent the basic unit of computations. To efficiently leverage the allocated resources, the application needs to consider various factors. Some factors to consider are trustworthy and stable, such as the application structure or the topology of the allocated resources of the platform. Other factors can only be unreliably measured, such as the effective processing time or the interconnect (internal buses or platform network). Moreover, the execution of an application is perturbed by factors alien to the application [Bha+13]. For example, an application may share some bandwidth with other applications, the temperature of the platform may raise and degrade performance due to other overdemanding applications, etc.

Facing such uncertainties, there is a need for simple, robust and context-aware scheduling policies. These policies also need to be able to handle the heterogeneity in the computing resources. There exist scheduling policies based on strip packing problems that provide efficient solutions with provable approximation ratios [Bou+11]. However, these policies are not robust as they require very precise estimations of the time to process tasks, but such estimations do not exist [HC16].

Locality is a well-known mechanism that drastically improves the execution performance. We propose to bring context-awareness through *contextual affinity*, which we define as a score derived from rough measures of the context (e.g., memory usage at a given moment). Each task prioritizes the computing resources it may be executed on with this qualitative score, and this serves as a guide for the scheduler.

Still, as of today, the application knowledge of the platform is limited to its allocated resources. However, as the platform is shared by several applications, it is not sufficient to consider the intra-application level.

# 1.2.2 Inter-Applications Level

As stated earlier, HPC platforms now include millions of computing nodes. Very few applications, if any, are able to leverage that many resources. It is however crucial to maintain a high utilization of the platform. Hence, many applications are executed

simultaneously. Similarly to the tasks at the intra-application level, applications are competing for the computing and the communication resources. Yet, when working at this level, the core concept is the single application, and we do not care about too detailed a description of the applications.

As the platforms and applications grow in size, the amount of data transiting increases. Still, even if the memory density increases, the computing nodes cannot keep the whole datasets in their local memories. These datasets are hence stored on parallel file systems (e.g., Lustre) that reside on dedicated hardware. To ensure that the computing nodes can access data is the responsibility of the interconnection network. There exist various cost-effective and efficient interconnection topologies: multidimensional torus, fat-tree, SlimFly, DragonFly [Kat+15]. Such interconnection networks are meant to be unique and all-purpose within the platforms. Consequently, intra-application communications and I/O traffic have to share a global network: this induces complex interactions such as network contention between applications.

These nocuous interactions can either be tackled once applications have been scheduled (reactive strategy) or while scheduling them (proactive strategy). A typical reactive strategy would be—given some application allocations—to schedule the data movements [Gai+15]. On the other hand, a proactive strategy would tackle the interactions by enforcing smart allocations. With these smart allocations, the applications would induce less traffic. It is worth noticing that reactive strategies need a fine knowledge of the context, while proactive strategies do not.

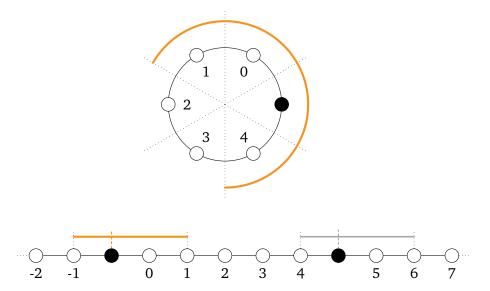

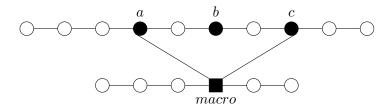

We consider context in an oblivious manner at this inter-application level. Rather than optimizing communications once the applications have been scheduled, we propose to enforce constraints on the allocations. These constraints allow us to completely abstract the context of execution while guaranteeing the applications will behave well by isolating them.

# 1.3 Explicit vs. Implicit Modeling of Communications

The 2010 Turing award laureate, Leslie Valiant, described a good model as a bridge between the chosen programming model and the hardware [Val90]. More precisely, a good model has to be "easy to implement in hardware" and "efficiently targeted by programmers". As an example, the von Neumann model (a.k.a. RAM model) of the computer is a very good abstraction for sequential programming. On the other hand, the search for a good parallel programming model is still going on.

#### 1.3.1 Existing Explicit Models

**PRAM** The natural extension of the von Neumann model for parallel platform is the PRAM model (Parallel Random-Access Machine) [FW78]. A parallel platform is modeled as an unbounded number of processors with access to an unbounded global memory. At each step in this model, the processors simultaneously execute three successive operations: an optional read, followed by a computation, finished by an optional write. Despite being a powerful classification tool, the PRAM model ignores the communications cost and the synchronization overhead, and it is not representative of modern parallel platforms.

To overcome this weakness of the PRAM model, many modeling approaches have been proposed. We quickly review three classical model families aiming at integrating communication: communication delays, BSP, and LogP.

**Communication Delays** The communication delays modeling techniques rely on the representation of a computation as a directed acyclic graph of dependencies: vertices represent computations, and edges represent data dependencies between computations. A parallel platform is modeled as a set of processors with local memory connected by an interconnection network. Following the edges of the dependency graph, a data exchange is delayed if the computations are not scheduled on the same processor. A review of various models with communication delays can be found in [BGT97].

**BSP** The BSP model (**B**ulk **S**ynchronous **P**arallel) has been proposed in the 1980s by Valiant [Val90]. The BSP model integrates the communication from a macroscopic point of view. A parallel platform is modeled as a set of processors, a network to exchange messages, and some hardware support for synchronization. The computations under BSP are modeled as a series of supersteps: each superstep consists in a phase of concurrent computations, a phase of global communications, and a synchronization phase.

**LogP** The LogP model tackles the issue of communications from an architectural point of view [Cul+93]. A parallel platform under LogP is modeled as a set of processors communicating thanks to an interconnection network. However, contrarily to the BSP model, the processors communicate asynchronously with messages of small size (e.g., 16 bytes in [Dus+96]). The time to exchange messages is then

modeled with three parameters: the latency of the network, the overhead (time spent to process a message) and the gap (reciprocal of the network bandwidth).

#### 1.3.2 Limits of Explicit Models

Parallel platforms are complex systems, where integrating more and more components emphasizes some unforeseen patterns. Existing models exhibit various limitations that prohibit their use at the extreme scales we target. Explicit modeling of the communications faces the issue of choosing between models that are too precise or too coarse.

Too precise models are unable to scale due to the number of parameters needed to apprehend the exascale. Moreover, gathering valid data to instantiate models is an arduous task: the volume of data is tremendous, the granularity of measures is often too coarse to get useful data, instrumentation of code is tedious, etc. Furthermore, the patterns of application submission times are ever-changing: they depend, for example, on the day of the week, whether the location of a conference is attractive or not, how tight the next deadline is. Such behaviors are barely quantifiable. In light of these points, what is the purpose of having ultraprecise model when we are unable to instantiate them?

On the other side of the spectrum, coarse models are unable to capture phenomena such as contention. For example, the BSP model makes the assumption that the network is in a steady state by considering the "basic throughput [...] when in continuous use" [Val90]. This assumption presupposes the latency in the interconnection network can be bound: this is at best a very imprecise assumption, at worst a false hypothesis. Thus, the contention on networks is either imprecisely modeled, or falsely taken into account. Although the LogP model cannot be considered a coarse grain model, it is flawed as it makes the assumption that the bandwidth is sufficient with respect to the message sizes.

# 1.3.3 Implicit Modeling

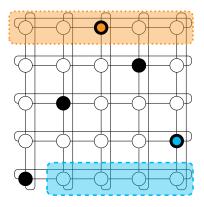

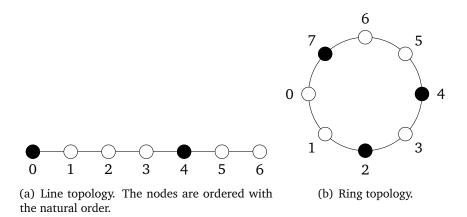

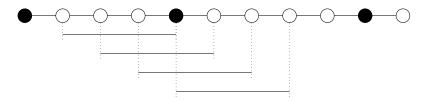

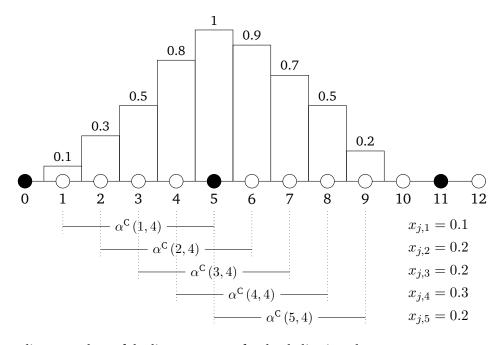

As stated in the previous section, explicit models are unable by design to capture contention at scale. Precise models are unable to scale as the number of parameters to account for explodes, while coarse models are too simple to model contention. The goal is instead to find a good balance between the two worlds, by keeping the simplicity of coarse models while capturing phenomena such as contention.